INCLUDING DEFENSE TECH WIRE

INCLUDING DEFENS

John McHale ITAR fines

Field Intelligence

Honey I shrunk the data center

Mil Tech Insider

Managing COTS ITAR compliance

# See also: Payload requirements drive rad-hard electronics

#### That's the nature of the AB2000 Avionics BusBox®

With so many built-in capabilities, the highly-flexible AB2000 family from Ballard Technology is the ideal fit for a wide range of applications. These rugged, conduction-cooled, COTS devices combine a powerful computer processor, multi-protocol databus interfaces, Ethernet, USB, other I/O, and PMC expansion in a small, lightweight package.

#### Discover what the AB2000 can do for you.

Visit our website or call 425.339.0281 for more information.

AN ASTRONICS COMPANY

#### AB2000 Personalities...

- · Embedded Computer

- · Aircraft Interface Device

- · Data Recorder

- · Protocol Converter

- · Ethernet Switch

- · Power Management Unit

- · Radio/Satcom Interface

- · and many more

www.ballardtech.com/AB2000

### Annapolis Micro Systems

The FPGA Systems Performance Leader

## High Performance Signal and Data Processing in Scalable FPGA Computing Fabric

GEOINT, Ground Stations, SDR, Radar, Sigint, COMINT, ELINT, DSP, Network Analysis, Encryption, Image Processing, Pattern Matching, Oil & Gas Exploration, Financial Algorithms, Genomic Algorithms

Direct Seamless Connections with no Data Reduction Between External Sensors and FPGAs Between FPGAs and Processors over IB or 10GE Between FPGAs and Standard Output Modules Between FPGAs and Storage Arrays

Ultimate Modularity

From 1 to 8 Virtex 4, 5 or 6 FPGA/Memory Modules

Input/Output Modules Include:

Quad 130 MSPS thru Quad 550 MSPS A/D

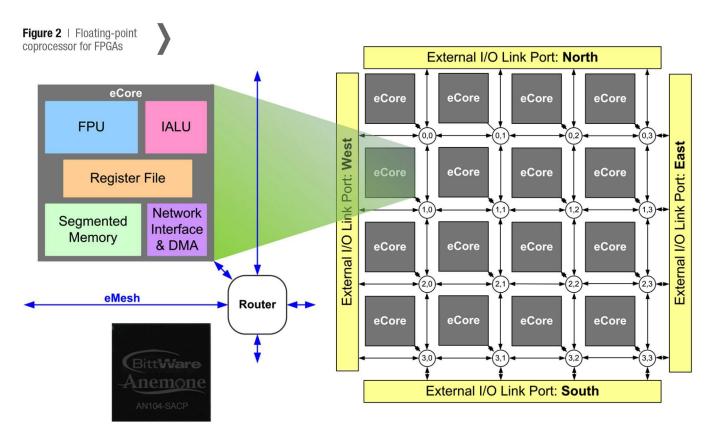

1.5 GSps thru 5.0 GSps A/D, Quad 600 MSps D/A,

Dual 1.5 GSps thru 4.0 GSps D/A

Infiniband, 10G, 40G or 100G Ethernet or SFPDP

VME/VXS/VPX, IBM Blade, PCI-X/PCI Express, PMC/XMC, MicroTCA

No Other FPGA Board Vendor Streams This Volume of Data Real Time Straight Into the Heart of the Processing Elements and Then Straight Back Out Again

190 Admiral Cochrane Drive, Suite 130, Annapolis, Maryland USA 21401 wfinfo@annapmicro.com USA (410) 841-2514 www.annapmicro.com

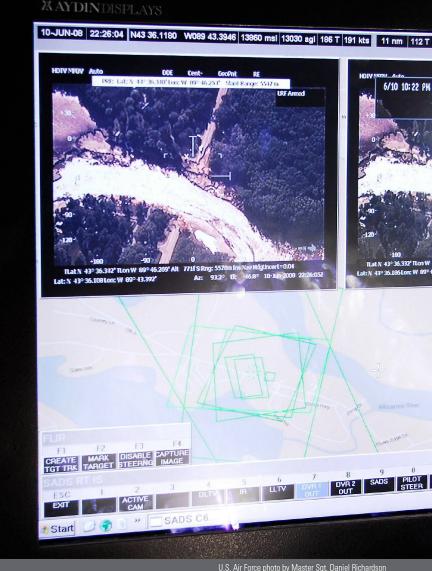

## www.mil-embedded.com Vilitar EMBEDDED SYSTEMS

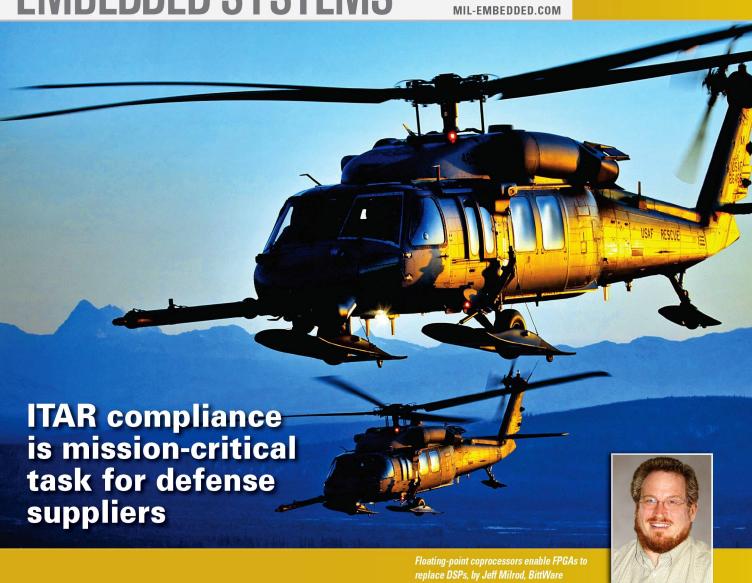

#### ON THE COVER:

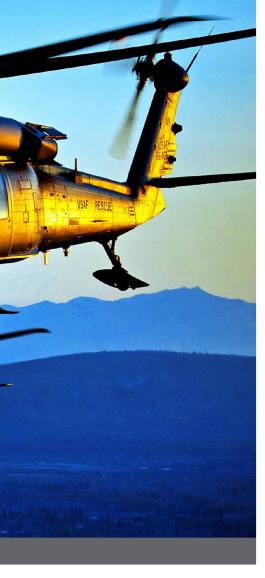

Top photo: An Alaska Air National Guard HH-60G Pave Hawk helicopter crew practices flight formation maneuvers over Joint Base Elmendorf-Richardson, Alaska, March 14, 2012. U.S. Air Force photo by Master Sgt. Sean Mitchell.

Bottom photo: The GPS III satellite from Lockheed Martin makes use of radiation-hardened electronics for its payload and control systems. Photo courtesy of Northrop Grumman, whose Astro Aerospace business unit supplies self-deploying, monopole JIB antennae for the satellite.

June 2012 Volume Numbe

#### COLUMNS

#### **Editor's Perspective**

ITAR fines can cripple your business By John McHale

#### Field Intelligence

Honey, I shrunk the data center 10 By Charlotte Adams

#### Mil Tech Insider

Managing ITAR compliance in COTS systems design By Curtis Reichenfeld

#### **DEPARTMENTS**

14-15 Defense Tech Wire By Sharon Hess

#### **EVENTS**

www.opensystemsmedia.com/events

#### 2012 IEEE Nuclear and Space Radiation **Effects Conference**

July 16-20, 2012 • Miami, Florida www.nsrec.com/regist.htm

#### **AUVSI's Unmanned Systems** North America 2012

August 6-9, 2012 • Las Vegas, Nevada www.auvsishow.org

#### **WEB RESOURCES**

Subscribe to the magazine or E-letter Live industry news | Submit new products http://submit.opensystemsmedia.com

White papers:

Read: http://whitepapers.opensystemsmedia.com Submit: http://submit.opensystemsmedia.com

All registered brands and trademarks within Military Embedded Systems magazine are the property of their respective owners.

© 2012 OpenSystems Media © 2012 Military Embedded Systems ISSN: Print 1557-3222

#### SPECIAL REPORT | Managing ITAR and import/export issues

ITAR compliance is a mission-critical task for defense suppliers By John McHale

#### MIL TECH TRENDS | Rad-hard electronics for mil space systems

- 20 Military satellite payload performance demands drive rad-hard electronics By John McHale

- 24 Rad-hard SRAM FPGAs enable vast improvements in space exploration By John D. Corbett and Gary M. Swift, Xilinx

#### **INDUSTRY SPOTLIGHT** | FPGA trends for mil systems

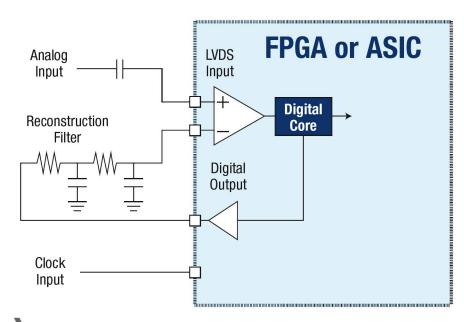

- Implementing analog functions in rugged and rad-hard FPGAs 28 By Allan Chin and Luciano Zoso, Stellamar

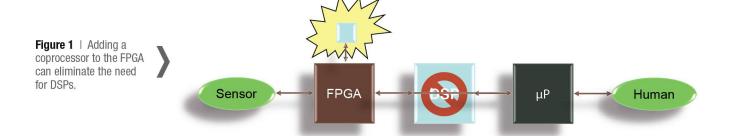

- 32 Floating-point coprocessors enable FPGAs to replace DSPs By Jeff Milrod, BittWare

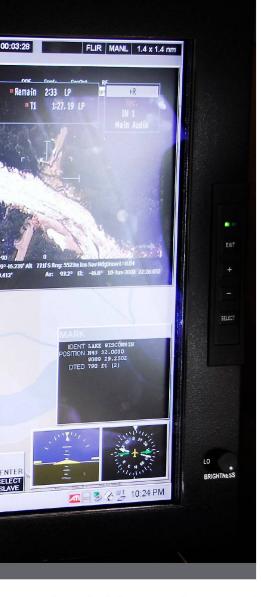

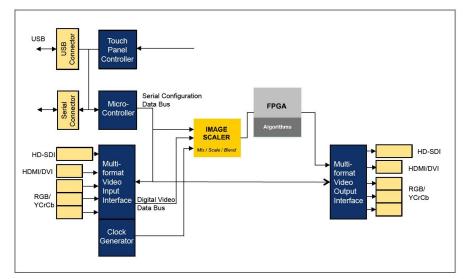

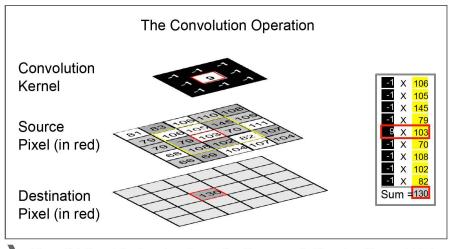

- FPGA-powered display controllers enhance ISR video in real time 38 By Jason Wade and Randall Millar, Z Microsystems

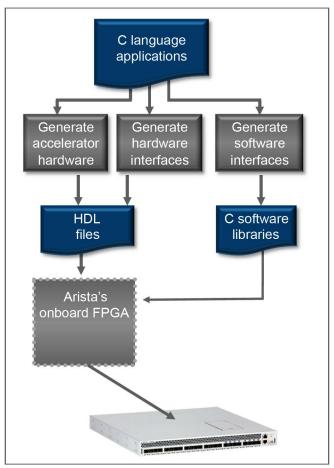

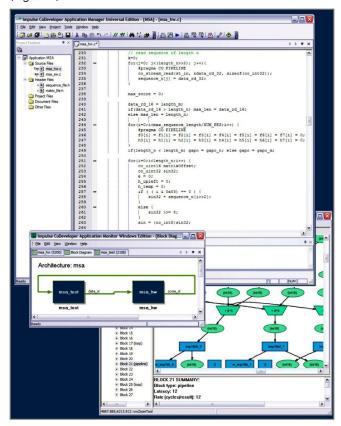

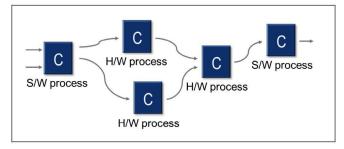

- 42 From Wall Street to the military: Advances in FPGA switching technology and software-to-hardware development tools facilitate wire-speed data transmission By Douglas Gourlay, Arista Networks and Brian Durwood, Impulse Accelerated Technologies

## YOUR OFFICE. OUR ROUTER.

CISCO Technology

Utilizing the same Cisco IOS software that IT staffs are already trained on, our rugged, SWaP optimized routers are battlefield-ready. The X-ES XPedite5205 PMC router module and the SFFR small form factor

router platform, working in conjunction with UHF, VHF, Wi-Fi and other radio platforms create mobile ad hoc networks to provide highly secure data, voice and video communications to stationary and mobile network nodes across both wired and wireless links. **Call us today to learn more.**

X-ES

**Extreme Engineering Solutions** 608.833.1155 www.xes-inc.com

Connected everywhere. That's Extreme.

#### ADVERTISER INFORMATION

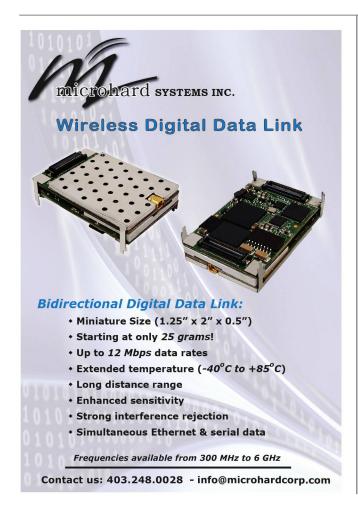

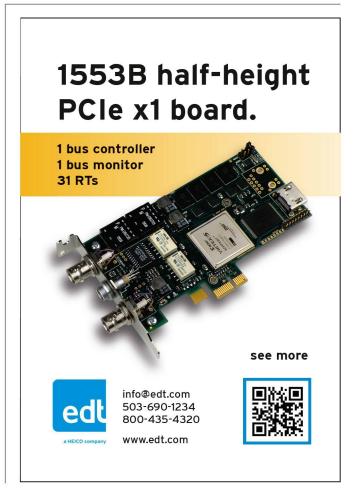

#### Advertiser/Ad Title Page 3 Annapolis Micro Systems, Inc. – High performance signal and data processing 46 **Association for Unmanned Vehicle Systems International** (AUVSI) - AUVSI's Unmanned Systems North America 2012 2 **Ballard Technology** – A surprising blend of personalities D-TA Systems - Record/playback 9 at record breaking speed 31 ELMA Electronic - ELMA's FPGA reference platform has got your back ... and your front EDT Inc. - 1553B half-height PCle 33 x1 board 19 Excalibur Systems, Inc. - Dragon It's not a myth 5 Extreme Engineering Solutions -Your office. Our router. GE Intelligent Platforms, Inc. -47 When sensor data volumes become overwhelming, rely on GE 21 General Standards Corporation -High reliability I/O boards designed to work for you 11 **Hypertronics** – Hypertronics rugged connector series 13 Innovative Integration – Radar wireless solutions 30 Microhard Systems, Inc. -Wireless digital data link Nallatech - FPGA acceleration 26 40 Parvus Corporation -Cisco technology - ruggedized 48 Pentek, Inc. - Got tough software radio design challenges? 30 Phoenix International – Solid or spin ... we go both ways Vector Electronics & Technology,

## Military EMBEDDED SYSTEMS

#### Military Embedded Systems Editorial/Production Staff

John McHale, Editorial Director imchale@opensystemsmedia.com

Sharon Hess, Managing Editor sharon\_hess@opensystemsmedia.com Terri Thorson, Senior Editor (columns) tthorson@opensystemsmedia.com Steph Sweet, Creative Director

#### Sales Group

Tom Varcie Senior Account Manager tvarcie@opensystemsmedia.com

Rebecca Barker Strategic Account Manager rbarker@opensystemsmedia.com

Eric Henry Strategic Account Manager ehenry@opensystemsmedia.com

Ann Jesse Strategic Account Manager ajesse@opensystemsmedia.com

Christine Long Director of Online Development clong@opensystemsmedia.com

#### International Sales

Elvi Lee, Account Manager - Asia elvi@aceforum.com.tw

ssweet@opensystemsmedia.com

#### Regional Sales Managers

Barbara Quinlan Midwest/Southwest bquinlan@opensystemsmedia.com

Denis Seger Southern California dseger@opensystemsmedia.com

Sydele Starr Northern California sstarr@opensystemsmedia.com

Ron Taylor East Coast/Mid Atlantic rtaylor@opensystemsmedia.com

#### Reprints and PDFs

republish@opensystemsmedia.com

#### OpenSystems Media Editorial/Production Staff

Mike Demler, Editorial Director DSP-FPGA.com mdemler@opensystemsmedia.com

Joe Pavlat, Editorial Director CompactPCI, AdvancedTCA, & MicroTCA Systems ipavlat@opensystemsmedia.com

Jerry Gipper, Editorial Director VITA Technologies jgipper@opensystemsmedia.com

Warren Webb, Editorial Director Embedded Computing Design Industrial Embedded Systems wwebb@opensystemsmedia.com

Jennifer Hesse, Managing Editor Embedded Computing Design Industrial Embedded Systems jhesse@opensystemsmedia.com

Sharon Hess, Managing Editor VITA Technologies sharon\_hess@opensystemsmedia.com

Monique DeVoe, Assistant Managing Editor PC/104 and Small Form Factors DSP-FPGA.com

mdevoe@opensystemsmedia.com

Brandon Lewis, Associate Editor CompactPCI, AdvancedTCA, & MicroTCA Systems blewis@opensystemsmedia.com

Curt Schwaderer, Technology Editor

Steph Sweet, Creative Director

David Diomede, Art Director

Joann Toth, Senior Designer

Konrad Witte, Senior Web Developer

Matt Jones, Web Developer

#### **Editorial/Business Office**

Patrick Hopper, Publisher Tel: 586-415-6500 phopper@opensystemsmedia.com

#### **Subscriptions Updates**

Karen Layman, Business Manager www.opensystemsmedia.com/subscriptions Tel: 586-415-6500 ■ Fax: 586-415-4882 30233 Jefferson, St. Clair Shores, MI 48082 Rosemary Kristoff, President rkristoff@opensystemsmedia.com

Wayne Kristoff, CTO

16626 E. Avenue of the Fountains, Ste. 201 Fountain Hills, AZ 85268 Tel: 480-967-5581 ■ Fax: 480-837-6466

35

7

37

Experience unprecedented clarity

Inc. - VME/cPCI ruggedized

WinSystems, Inc. – A 1.66 GHz

Z Microsystems, Inc. -

Intel Atom Mil/COTS SBC of EPIC

chassis

proportions

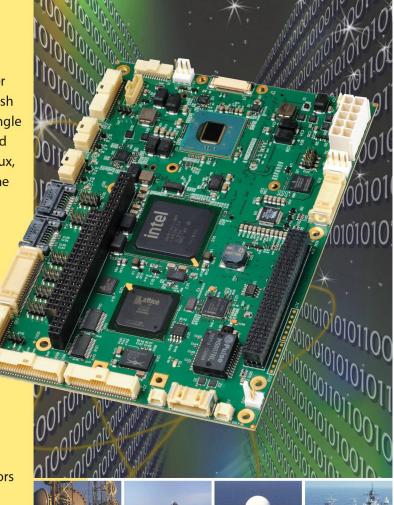

A 1.66GHz Intel®Atom™ Mil/COTS SBC of EPIC Proportions

The EPX-C380 is a rugged single board computer that provides an open powerful platform for harsh Mil/COTS applications. Powered with either a single or dual core processor, it has a wealth of onboard I/O plus expansion options. Also it supports Linux, Windows® XP embedded, and other x86 real-time operating systems.

1.66GHz Intel® Atom™ N450 single core or D510 dual core processor available

Embedded Gen 3.5+ GFX video core supports CRT and LVDS flat panels simultaneously

- · Custom splash screen on start up

- Optional 1MB of battery backed SRAM

- Two Gigabit Ethernet ports

- Two SATA channels

- · Eight USB 2.0 ports

- · Four serial RS-232/422/485 channels

- 48 bi-directional digital I/O lines

- CompactFlash (CF) card supported

- MiniPCle and PC/104-Plus expansion connectors

- High Definition audio supported (7.1)

- WDT, RTC, LPT, status LEDs, and beeper

- +5 volt only operation

- EPIC sized: 4.5" x 6.5" and RoHS compliant

- EBX form factor SBC also available

- Extended temperature operation

- Responsive and knowledgeable technical support

- Long-term product availability

- · Quick Start Kits for software development

Contact us for additional information, pricing, and custom configurations. Our factory application engineers look forward to working with you.

Call 817-274-7553 or Visit www.winsystems.com/EPX-C380MR

Ask about our 30-day product evaluation

715 Stadium Drive • Arlington, Texas 76011 Phone 817-274-7553 • FAX 817-548-1358 E-mail: info@winsystems.com

#### ITAR fines can cripple your business

By John McHale, Editorial Director

Many in the defense industry community are familiar with export regulations such as the International Traffic in Arms Regulations or ITAR and the nasty punishments the government will level against those who neglect to comply or fail to obtain the proper licenses. However, newcomers to this market might not know how severe the penalties for export compliance missteps can be.

Recent punishments have ranged from \$20,000 to as much as \$78 million. Yes, you read that correctly - \$78 million. Not only that: If you are being investigated for a potential ITAR violation, the State Department can shut down your operation, preventing you from shipping or receiving products. While the Obama administration is exploring various export reform initiatives, the increased enforcement of these regulations is unlikely to abate any time soon. There is also no shortage of enforcement officers, and they like to keep busy.

Detailed listings of fines and ITAR violations can be found at this State Department website: www.pmddtc. state.gov/compliance/consent agreements.html. I've summarized a couple of the larger one's fines/punishments here, such as the hefty \$78 million civil penalty that was leveled against BAE Systems in 2011.

The Department of State charged BAE Systems plc - not the North America subsidiary, BAE Systems Inc., - with violations of the Arms Export Control Act (AECA) and ITAR - 2,591 violations in total and as far back as 1995. Some of the violations included failure to obtain U.S. State Department approval "to engage in brokering activities of the U.S. systems or subsystems" on platforms including the Hawk Trainer aircraft, the EF-2000 Eurofighter Typhoon, and the Saab Gripen aircraft prior to the sale of those aircraft to multiple foreign nations,

according to the Department of State proposed charging letter to BAE Systems from May 2011. In other words, any time electronics on the U.S. Munitions List (USML) are added or modified, proper approval must be obtained before companies can export the systems.

Companies are not the only perpetrators that get nailed by the government for export violations. Individuals charged under AECA or ITAR can get extensive iail time because this is a crime. The victim of the crime is the soldier, marine, sailor, pilot, or airman whose life might be endangered by American technology falling into the wrong hands.

"While the Obama administration is exploring various export reform initiatives, the increased enforcement of these regulations is unlikely to abate any time soon. There is also no shortage of enforcement officers, and they like to keep busy."

Examples where jail time was handed out can be found on the State Department's website in a Justice Department pdf document that covers major U.S. export enforcement and embargo criminal cases dating back to 2007 (www.pmddtc.state.gov/compliance/ documentsOngoingExportCaseFact Sheet.pdf). Check it out, it reads like a police blotter.

One of those cases, dated December 3, 2010, details the illegal sale of radiationhardened (rad-hard) semiconductor components to China. Lian Yang of Woodinville, WA, was arrested and charged with conspiracy to violate the

AECA by attempting to purchase and export from the U.S. to China 300 radhard, programmable semiconductor devices, which are classified as defense articles under the U.S. Munitions List. According to the Justice Department document, Yang and his co-conspirators were busted in an undercover operation when they wire-transferred \$60,000 to undercover agents for partial payment on some of the devices. Agents from ICE, CBP, and the FBI conducted the investigation. (To read about law-abiding rad-hard electronics suppliers, see our Mil Tech Trends section, beginning on page 20.)

U.S. export controls, while useful in protecting American technology from roque nations, have also been a detriment for defense technology suppliers wanting to be competitive on a global scale – especially in the commercial satellite industry. The DoD and industry are currently lobbying Congress to have satellites and related devices not containing technology vital to the U.S. military taken off the U.S. Munitions List and designated as dual-use items on the Commerce Control List (CCL). This would be a huge boost to U.S. satellite component designers who want to grow their business but feel handcuffed by ITAR regulations. The effort is called the 1248 Report and is covered in our Special Report on ITAR compliance, beginning on page 16. Also in that article, export attorney Kay Georgi of Arent Fox, LLP, talks about the latest enforcement trends and gives tips on how to set up a compliance program.

The best tip I heard was from an attendee at an ITAR panel discussion a few years ago: Assume everything is ITAR-controlled and cover your back because you don't want to get that letter from the State Department.

John McHale imchale@opensystemsmedia.com

### Record/Playback @ Record Breaking Speed...

**D-TA'S 10 GIGABIT SENSOR PROCESSING (10 GSP)** implementation has revolutionized sensor processing by offering **limitless scalability** that allows the throughput rate to increase linearly as more networks (fibers) are added, and **totally synchronized operation** that ensures the data is precisely time synchronized across all fibers, irrespective of the number of fibers.

## Record/Playback@over 800 MBytes/s with 1 fiber

## Record/Playback @ over 2 GBytes/s with 2 fibers

Leveraging our 10 GSP concept, we have developed a generic record / playback configuration that measures up to your requirements. Radio, radar, sonar, acoustic — whatever your application, we likely have an end-to-end solution from signal acquisition to record & playback.

## Record/Playback @ over 4 GBytes/s with 4 fibers

2 X DTA-5000 (6U & 19.2 TB SAS Drives) [64 TB with SATA]

We are delivering recording solutions that sustain over 8 GBytes/s using 8 fibers and 4 DTA-5000 units.

For more information, click the Recording at Record Breaking Speed button on our home page at www.d-ta.com

#### Honey, I shrunk the data center

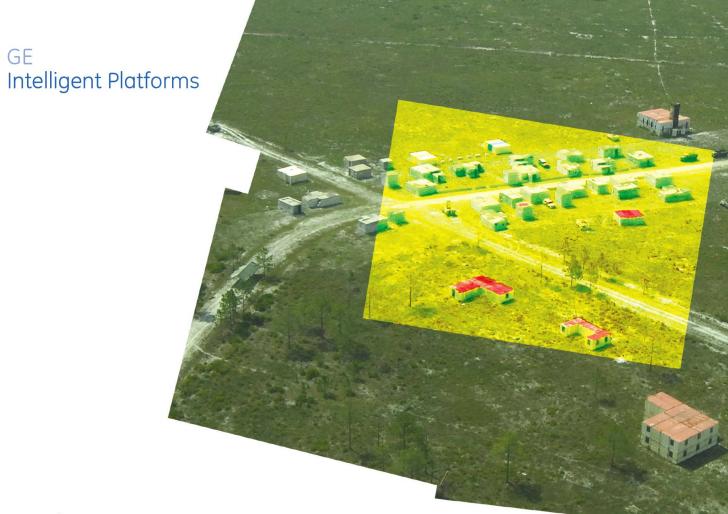

By Charlotte Adams A GE Intelligent Platforms perspective on embedded military electronics trends

Why are defense chip and board developers turning to the InfiniBand switched fabric interconnect technology? Though blazing fast, InfiniBand is neither new nor widely used in Department of Defense (DoD) weapons and platforms. But a new InfiniBand-on-VPX paradigm is coming to high-performance embedded computing to meet the needs of Intelligence, Surveillance, and Reconnaissance (ISR) and similar demanding applications.

#### Advantage of InfiniBand

InfiniBand provides high-speed, point-to-point bidirectional serial links between fabric nodes. The reason it is becoming attractive in high-performance embedded computing is because of InfiniBand's market penetration into platforms such as the top 500 high-performance computing clusters, large data centers, market trading floors, and cloud computing environments.

In fact, according to a press release from the InfiniBand Trade Association late last year, 42 percent of the world's most powerful computers listed at www.top500.org use InfiniBand. The number of cores connected via InfiniBand has increased 24 percent year on year. These platforms, some of which comprise tens of thousands of Intel and NVIDIA processors, have driven the development of extremely robust software support at the operating system, middleware, and driver levels.

#### VPX and InfiniBand

Developers are also combining InfiniBand with VPX, a pointto-point serial backplane interconnect that is the migration path for VME. VPX shares form factors with VME but has many advantages over the workhorse parallel bus used in many embedded military and aerospace applications. VPX offers at least an order of magnitude increase in data rates over VME. Although each VPX link sends only a few bits at a time, the data rate is so high that card-to-card transfers can reach more than 100 GBps. Additionally, multiple receivers and transmitters can communicate at the same time.

VPX is a multiplane technology that allows data crunching, expansion, control, management, and utility tasks to be executed separately and simultaneously on their respective planes, improving overall speed and efficiency. VPX is also agnostic to physical protocols, making it highly flexible. For example, on the data plane, designers can implement InfiniBand, 10 GbE, PCI Express, or Serial RapidIO. VPX is flexible, offering a wide range of possible architectures. Indeed, so wide is the possible range of architectures that VITA, the VME trade association, has formed an umbrella OpenVPX (VITA 65) working group to develop a set of standard backplane topologies to facilitate the development of modular open-system architectures.

Figure 1 | The SBC625 from GE Intelligent Platforms, a 6U VPX board using Intel's 2.3 GHz Core i7-3615QE

#### Ripe ecosystem

The InfiniBand software ecosystem, there for the taking, begs to be used by the high-performance applications typical of many military and aerospace projects. It correlates directly with the DoD's need, now more than ever, to exploit commercial development, minimize costs, and protect existing investments.

Driving adoption are data-hungry but space-constrained applications in areas such as ISR, signals intelligence, electronic warfare, and communications. For example, relatively small packages on drones are expected to crunch floods of data from front-end sensors and provide actionable information in real time. To do that, they need not only higher data throughput but higher interboard communications, for which InfiniBand-on-VPX offers an attractive solution. Drones are just one potential platform. Others include aircraft, submarine, and satellite sensors where high speed and bandwidth are needed but real estate is scarce.

#### Ready for prime time

A number of embedded computing developers are working on InfiniBand/VPX products in combination with Intel's latest Core i7 products. A case in point is the SBC625 from GE Intelligent Platforms, a 6U VPX board using Intel's 2.3 GHz Core i7-3615QE processor (Figure 1).

InfiniBand is optimized for very high-throughput, low-latency data traffic. It fits well with multicore processors and supports Remote Direct Memory Access (RDMA), General-Purpose Computing on Graphics Processing Units (GPGPU), and Open Fabrics Enterprise Distribution (OFED) open-source software, among other advantages.

According to the InfiniBand Trade Association, OFED adoption and deployment are increasing, largely because it helps RDMA-based networks provide computing efficiencies as high as 96 percent and latencies as low as 1 microsecond, as well as reducing data center power consumption by up to 50 percent.

The bottom line is that InfiniBand with VPX brings together the software created for high-performance supercomputers in a rugged, backward-compatible format, creating a powerful synergy for defense and aerospace applications.

Contact Charlotte at cburtonadams@yahoo.com.

Answering Market Demands for Dependable Interconnect Solutions in Extreme Environments

## Hypertronics Rugged Connector Series

#### Dependable Connectors with Reliable Technology:

Hypertac Hyperboloid, Spring Probe, Fiber Optic, Hi-Speed Filtering, or Custom Tailored to Meet Your Specifications

HYPERTRONICS: RELIABLE CONNECTORS. DEPENDABLE SOLUTIONS.

HYPERTRONICS CORPORATION

Hudson, MA 1-800-225-9228 ISO9001, ISO14001, AS9100 and OHSAS18001

#### Managing ITAR compliance in **COTS** systems design

By Curtis Reichenfeld An industry perspective from Curtiss-Wright Controls Defense Solutions

As foreign sales continue to be a key driver for many U.S. vendors, it is critical to ensure due diligence of the International Traffic in Arms Regulations (ITAR) to avoid profile violations and penalties.

ITAR is the set of export control regulations implemented and enforced by the U.S. State Department's Directorate of Defense Trade Controls (DDTC) that controls the export of defense articles, defense services, and technical data as designated on the U.S. Munitions List (USML). Under ITAR, defense articles are items specifically designed, developed, or manufactured for military or defense purposes. These include commercial items that have been modified for a military purpose. Certain technical assistance services related to defense or military purposes are known as defense services. Defense services can include activities such as repairs, training, engineering, testing, and product assembly. Technical data might include documents, drawings, schematics, design information, data sheets, and so on that reveal technical data directly relating to items on the USML.

The U.S. Department of Commerce's Bureau of Industry and Security (BIS) implements and enforces the Export Administration Regulations (EAR) that regulate the export and re-export of most commercial items. This includes "dual-use" items with both commercial and military or proliferation applications. It also includes purely commercial items without obvious military use. License requirements depend upon an item's technical characteristics, the destination, the end user, and the end use. The exporter must make the determination if an export requires a license. While other regulations can be relevant, the EAR and ITAR are the most frequently applied and regularly encountered sources of control for high-technology industries.

Typically, manufacturers can self-classify their items by reviewing the ITAR and EAR. If the manufacturer is uncertain of an item's classification, they can get assistance by submitting a Commodity Jurisdiction (CJ) request to DDTC. A CJ is a process that outlines how export control jurisdiction is determined, which is the first step in analyzing an item's overall export control classification. DDTC, in cooperation with BIS, can classify the product as "dual use," which includes civil and some military applications, or "commercial," and can further provide the full classification number. Neither dual-use items nor commercial items fall under the ITAR.

#### Product development process

ITAR issues should be considered during the product development process, before design and manufacture, to ensure equipment is ITAR free. At Curtiss-Wright Controls Defense Solutions, during the first part of an IRAD approval process, we focus on a product's high-level requirements. Product descriptions should be written with the ITAR in mind and then reviewed by export compliance experts. Involve the export

control officer early to make a determination if the product can be classified as ITAR free.

During product design, use commercially available components and software algorithms to reduce the risk that the product can fall under the ITAR. If commercial parts are not available or the application requires military-grade chips, companies need to follow the regulations and can apply for a CJ.

#### Common mistakes

Some of the common compliance errors COTS vendors need to avoid include:

- > Failure to hire a compliance expert Hiring a dedicated export control officer experienced in working with the Department of State and ITAR is essential for ensuring compliance.

- Failure to maintain detailed records Start with an export compliance plan and keep detailed records documenting the plan implementation, including any self-classifying of products. CJ applications also require providing records of product background and sales information. Documentation associated with all exports of items or defense articles, defense services, and technical data must be retained by the exporter.

- Reclassification of products Legacy products might need to be reclassified as items fall off the ITAR USML or EAR Commerce Control List. Export control officers should review products regularly and determine if classification or application for a CJ is needed.

- > Too focused on sales Many companies, while focusing on sales and generating new business, lose sight of ITAR compliance. They need to dedicate the appropriate time for reviewing products and obtaining licenses in advance of a sale.

- Poor training Proper training and awareness ensure that employees understand ITAR compliance and know to ask the proper questions when they experience issues with products that could be controlled items. Companies need to document an export compliance plan that is tied to company procedures and then invest in training.

Ignorance of the ITAR is not a valid defense against violations of the regulations. When in doubt, apply for a CJ determination to ensure the jurisdiction of products and seek the assistance of an experienced export compliance person to determine export license requirements. With proper due diligence, new markets for U.S. companies are available worldwide.

This column is a synopsis of a high-level white paper written by Curtis. For more information, e-mail Curtis at Curtis.Reichenfeld@curtisswright.com.

## RADAR WIRELESS SOLUTIONS

#### GHz Analog I/O + FPGA

#### **Features**

Two 1 GSPS, 12-bit A/D channels Two 1 GSPS, 16-bit DAC channels

+/-1V, AC or DC -Coupled, 50 ohm, SMA I/O

Xilinx Virtex-6 SX315T/SX475T or LX240T

4 Banks of 1GB DRAM (4 GB total)

Ultra-low jitter programmable clock

Arbitrary Waveform Generation Memory

Controller for DACs

PCI 32-bit, 66 MHz with P4 to Host card

20-25W typical

Conduction Cooling per VITA 20

Ruggedization Levels for Wide Temperature Operation

Gen2 x8 PCI Express providing 2 GB/s sustained transfer rates

Adapters for VPX, Compact PCI, desktop PCI and cabled PCI Express systems

### DEFENSE TECH WIRE

By Sharon Hess, Managing Editor

mil-embedded.com/magazine/wire

NEWS | TRENDS | DoD SPENDS

#### U.S. Navy Trident II production occurs the conventional way

While fictional movie character Tony Stark of "Iron Man" fame made it look easy to make a missile-shooting armored exoskeleton while in captivity, in reality missile production is a complicated process requiring many resources. And apparently per a \$236 million U.S. Navy contract - semi-namesake real-life company Charles Stark Draper Laboratories, Inc. is slated to render alteration materials for the Trident II (D5) missile guidance systems' production (Figure 1). Work will ensue in El Segundo, CA; Clearwater, FL; Cambridge, MA; Pittsfield, MA; and Tarrytown, NY, and is anticipated for fulfillment by September 2016.

Figure 1 | A \$236 million U.S. Navy/Charles Stark Draper Laboratories, Inc. contract calls for alteration materials for Trident II (D5) guidance systems' production. U.S. Navy photo by Seaman Benjamin Crossley

#### Laser JDAM sensors to be onboard more military aircraft

The Boeing Company's Laser Joint Direct Attack Munition (Laser JDAM) sensors will soon find themselves on more U.S. military aircraft, per a \$12.5 million U.S. Naval Air Systems Command (NAVAIR)/Boeing contract. JDAM is a guidance kit that is "low cost" and transforms "existing unguided freefall bombs into near precision-guided weapons," according to the Boeing website. JDAM enables moving target, relocatable target, and maritime threat prosecution. The laser sensor added to traditional JDAM is a relatively straightforward option to implement for pilots who have been using conventional JDAM, Boeing reports.

#### Northrop Grumman to upgrade USAF production pods

The U.S. Air Force's pods are due for some sprucing up by Northrop Grumman Technical Services, thanks to a recent \$52 million pod upgrade program contract. The contract calls for "nonrecurring engineering services for [the] engineering manufacturing development phase," prototype upgraded pods (4),and modified support equipment sets (2); "low rate initial production support equipment will be a basic contract option manufacturing development phase," according to the DoD website. Northrop Grumman will also provide anywhere from 1 to 12 equipment kits for production pod support. Work occurs in Warner Robins, Georgia, and completion is anticipated in April 2017. The contracting activity is Robins Air Force Base in Georgia.

#### Test sets ensure USAF planes are in tip-top shape

All USAF aircraft must have their flight control systems tested; thus, a recent \$8 million contract between the USAF and Custom Manufacturing & Engineering, Inc. has the latter providing the former with flight control systems test sets that will be utilized by every Air Force program (Figure 2). "The flight control system test set tests, calibrates, and troubleshoots weapons systems equipment with reduced vertical separation minimum," the DoD website says. The test sets additionally generate static and regulated pilot pressures for use in analyzing pneumatic instruments, auxiliary equipment, and air data systems of the aircraft. Work is slated for completion in Pinellas Park, FL, by April 2018. The contracting activity is Robins Air Force Base in Georgia.

Figure 2 | A recent \$8 million USAF contract has Custom Manufacturing & Engineering, Inc. providing flight control systems test sets to be utilized by every USAF program. Pictured: The HH-60G Pave Hawk, U.S. Air Force photo by Master Sgt. Sean Mitchell

#### JSF hardware and software changes coming

Though they might appear identical at first glance, the U.S. Navy granted Lockheed Martin Corp. two differentyet-similar contract modifications on the same day: 1) A \$68 million modification for changes to baseline software and hardware configurations for the F-35 Lightning II Joint Strike Fighter/JSF (Figure 3); the government-requested alterations include short take-off vertical landing (USMC) and conventional landing and take-off (USAF) as a modification to an LRIP II contract. Funding comes from the U.S. Navy and USAF. 2) A nearly \$46 million F-35 Lightning II Joint Strike Fighter contract modification to an LRIP III contract also calls for baseline software and hardware changes, as required by the United Kingdom and the USMC for short take-off vertical landing. Funds are provided by the U.S. Navy and the U.K.

Figure 3 | Two recent contract modifications have Lockheed Martin making baseline software and hardware configuration changes to the JSF under LRIP II and III contracts. U.S. Navy photo of F-35C Lightning II JSF test aircraft courtesy of Lockheed Martin

#### ALQ-99 tactical jamming system's successor gets more mature

A recent \$20.5 million Naval Air Systems Command/ BAE Systems, Information and Electronic Systems Integration, Inc. contract modification stipulates that BAE renders next-generation jammer-supportive technology maturation. The next-generation jammer is, logically, slated as the successor to the aging tactical jamming system dubbed "ALQ-99." Efforts under the contract comprise research to enable future airborne electronic attack abilities proffered by an airborne stand-off/mod-escort platform that is tactical-sized. Thus, BAE will give Naval Air Systems Command a Concept Demonstrator (CD) design in addition to the needed mature technology elements that will support design of the Concept Demonstrator. Work takes place in Baltimore, MD; Lansdale, PA; Cincinnati, OH; Melbourne, FL; and Nashua, NH, and is anticipated to be done by April 2013.

> For consideration in Defense Tech Wire, submit your press releases at http://submit.opensystemsmedia.com. Submission does not guarantee inclusion.

Figure 4 | The U.S. Army and General Dynamics Land Systems signed a contract and a modification providing vehicles and technical services for Abrams tanks. M1A2 SEP V2 tanks photo by Mollie Miller, 1st Inf. Div. Public Affairs, U.S. Army

#### M1A2 Abrams spotlighted in contract and modification

The U.S. Army and General Dynamics Land Systems put pen to paper twice on one day, to benefit the venerable Abrams tank. First, a \$31 million contract calls for "the procurement of 46 Abrams M1A2 system enhancement package V2 vehicles [Figure 4]," with work slated for Anniston, AL; Scranton, PA; Lima, OH; and Tallahassee, FL, according to the DoD website. Work is anticipated for completion in November 2014. Second, a separate contract modification has General Dynamics Land Systems providing technical services for the Abrams Tank Program. Work is due for completion this December.

#### ASU to develop a health-monitoring system for warfighters

And the (contract) award goes to ... Arizona State University (ASU). Specifically, the Defense Threat Reduction Agency recently awarded ASU a Research, Development, Test, and Evaluation (RDT&E) contract comprising a 12-month performance base period with a \$9 million value in addition to a 36-month \$21,500 option. ASU's mission is to design a fieldable, chip-based, warfighter health-monitoring system prototype that can identify health changes of the warfighter (Figure 5). The goal is early infection detection. The contract's work will occur at Tempe, AZ.

Figure 5 | ASU will design a fieldable, chip-based, warfighter health-monitoring system prototype per a recent contract from the Defense Threat Reduction Agency, U.S. Army photo by Spc. Cassandra Monroe

#### **Special Report**

MANAGING ITAR AND IMPORT/EXPORT ISSUES

#### ITAR compliance is a mission-critical task for defense **suppliers**

By John McHale

Even though the U.S. government is entertaining various forms of export compliance control, defense suppliers must continue to be vigilant when dealing with the ITAR and other export regulations or face multimillion-dollar fines for failing to comply. Meanwhile, potential reforms to spacecraft export rules potentially could be a big win for rad-hard electronics vendors.

Producing embedded electronics for military applications requires that defense suppliers meet stringent environmental and performance standards on the design side so that the technology does not fail in the field. Compliance with U.S. export control regulations such as the International Traffic in Arms Regulations (ITAR) also is essential because failure to comply could lead to multimilliondollar fines that could shut down their business completely.

ITAR and export compliance regulations have been around for decades. but the past decade has seen record fines and increased enforcement of export controls by the U.S. government. Contributing to this are companies that have little experience with export compliance looking to break into the steady military market to stem losses in more volatile commercial markets.

Also many experienced companies think they know the difference between

a component that needs an ITAR license and one that does not or is classified as dual-use. "Dual-use has been used as a shorthand for describing items subject to the Export Administration Regulations (EAR)," says Kay Georgi, an export compliance attorney and Partner at Arent Fox LLP in Washington, D.C. Commerce in its proposed rule published July 15, 2011 "gave this definition: 'A dual-use item has commercial applications and also has military applications or proliferation concerns."

Enhanced export compliance enforcement makes it tough for U.S. companies to do business abroad in the global economy and also frustrates foreign companies looking to sell to the U.S. or to resell systems that have components of U.S. origin. The Obama Administration is working on overall compliance reform across multiple agencies, but these reforms still have to be approved by Congress.

#### Export compliance reform

"The Administration continues to make great progress towards developing a single control list," Georgi says. "To date, they have published proposed rules on: military aircraft; gas turbine engines; military vehicles; military vessels of war; submersibles; spacecraft through Report DoD 1248 from Departments of State and Commerce: and explosives and energetic materials, propellants, incendiary agents, and their constituents."

"These proposed rules would move many U.S. Munitions List (USML) controlled items to the Commerce Control List under special 600 Series Export Control Classification Numbers (ECCNs) that will continue to require licenses to most destinations, although some items may benefit from license exception Strategic Trade Authority (STA) for end use by the governments of some countries," Georgi says. "The proposed rules are still to be sent to Congress,

and of course, they still do not combine the Commerce Control List (CCL) and the USML into a single list. Indeed, some would say the addition of the 600 Series to the CCL effectively creates two lists within the CCL, but still these are substantial steps towards export control reform. A U.S. government official recently went on the record stating that the Administration hopes to send the necessary reports for a number of the USML categories to Congress as soon as August 2012. It remains to be seen if this ambitious schedule can be kept, as a number of proposed regulations need to be sent out for notice and comment first, but it indicates that the Administration continues to press forward briskly even in an election year."

#### Space export control policy reform: Section 1248 Report

The aforementioned Section 1248 Report is an effort by State and DoD officials working with the space industry to revamp space export control

policy. Congress requested the report in Section 1248 of the National Defense Authorization Act for Fiscal Year 2010 (Public Law 111-84), according to a DoD release.

"In the DoD 1248 report, the Departments of State and Defense concluded that certain satellites and parts and components did not warrant continued control on the USML," Georgi says. "More specifically: 'Communications satellites (COMSATs) that do not contain classified components; remote sensing satellites with performance parameters below certain thresholds; and systems, subsystems, parts, and components associated with these satellites and with performance parameters below thresholds specified for items remaining on the USML.""

"The current environment, which has rad-hard ICs covered under the ITAR, is destroying the satellite industrial base and is hurting the second- and thirdtier suppliers," says Chuck Tabbert, Vice President at Ultra Communications in Vista, CA, and a member of the President's Export Council Subcommittee on Export Administration (PECSEA). "If the recommendations of the 1248 Report are implemented, it could mean that radiation-hardened ICs will move to the Department of Commerce with a special export commodity control number, which by utilizing the new STA exception could allow us to ship to 36 nations without having a license required."

The Departments of State and Defense concluded that certain other satellites and parts and components did warrant continued USML control, such as satellites performing purely military or intelligence missions; remote sensing satellites with high-performance parameters; systems, subsystems, parts, and components unique to the aforementioned satellite types and not common to dualuse satellites; and services supporting foreign launch operations for USMLand CCL-designated satellites, Georgi says. To view the entire report, visit www.defense.gov/home/features/ 2011/0111 nsss/docs/1248 Report Space Export Control.pdf.

Tabbert says the reform will enable "friendly countries to sell to other friendly countries without getting U.S. permission first. They would be able to sell to European satellite manufacturers of COMSATs like Thales and EADS Astrium, which support Inmarsat, Eutelsat, etc. Another implication is that it will strengthen relationships with foreign partners. The government is still concerned about working with China in the space area, and the 1248 did not recommend a change to that practice."

The report essentially says that if even one U.S.-origin connector is on a Europeanmade satellite exported to China, it would require a license and be denied, Georgi says. "A license would still be required under the ITAR for a U.S. person to provide any assistance to a foreign person for a spacecraft to be launched from outside the U.S., even if that spacecraft may be exported under License Exception STA. Launch services and launch failure analysis for the CCL satellites and parts also remain subject to the ITAR," Georgi continues. "Since those selling spacecraft would normally need to provide some support for their launch, this effectively means that an ITAR license [presumably a Technical Assistance Agreement (TAA)] would still be needed to sell a U.S. CCL satellite to a non-U.S. or U.S. customer for launch outside the U.S."

#### Enforcement trends

"We are beginning to see the fruit of the export enforcement portion of the export control reform initiative in the creation of three cross-agency enforcement units," Georgi says. "How these coordination units will change the enforcement landscape remains to be seen, but I anticipate they will ensure a greater degree of coordination of efforts between the many agencies enforcing the export control laws."

One key coordination unit is the Export Enforcement Coordination Center (E2C2), which is housed at Immigration & Customs Enforcement and is a clearinghouse for coordinating enforcement activities among the Departments of Homeland Security, Commerce, Energy, Treasury, State, Justice, and the Director of National Intelligence, she says. A

second unit is the Information Triage Unit (ITU) in Bureau of Industry and Security that operates as a forum for assembling and disseminating information and intelligence gathered by agencies across the government so that individual export licensing agencies will have a consistent data set, Georgi continues. The third unit is the Office of the National Counterintelligence Executive (ONCIX), which coordinates export control issues involving the intelligence community.

"On the criminal side, I believe we are seeing greater crossover between export control cases and other cases, specifically in the areas of [the] Foreign Corrupt Practices Act (U.S. v. BAE Systems in 2010 and U.S. v. Shu Quan-Sheng in 2009) for ITAR Part 130 violations, the False Claims Act, and perhaps more than any other, the Economic Espionage Act (EEA)," Georgi continues. "While the EEA/export control prosecutions have largely targeted individuals, these have definitely been on the rise. In some cases, EEA prosecutions involve trade secrets that are not export controlled so there is not a perfect overlap between the two." For more on ITAR penalties, see the Editor's Perspective column on page 8.

A tough area for the government to enforce export violations is in cyberspace. Many small companies do not have the IT infrastructure to prevent access by unauthorized entities or persons, so "sophisticated intrusion attempts are on the increase, and some companies may choose to not report the attempt or actual intrusion, believing they may lose present or future business or create bad press," says Dean Young, Celestica Aerospace Technologies Corp. Security Manager in Austin, TX. Cloud services also risk that controlled data will inadvertently be released to unknown entities or countries without

#### **Export compliance in 15 steps**

Kay Georgi, an export compliance attorney and Partner at Arent Fox LLP in Washington, D.C., outlines 15 key steps to ITAR compliance.

- Get management buy-in for your compliance program - If management does not support the program, it likely will not work.

- Identify two persons in your organization who will be your export compliance personnel - one is not enough. If you do not have good candidates, you may have to recruit from outside your organization.

- Make sure your export compliance personnel have thorough export control training – For most companies except the largest, this usually means outside training.

- Classify all the products, services, software, and technology that your company exports. This might mean classifying all items, even if you do not "export" them in the traditional sense, if you employ foreign nationals or procure offshore. Put in your new product development a gate for classification, and put in your new contract review system a gate for classification.

- Make sure any controlled products are identified in your ERP system or in another fashion so that your personnel will know that they are controlled.

- Put in place automatic and other gates in your ERP system and in your sales/customer service departments to make sure that any controlled products are not exported, re-exported, imported (for items on the U.S. Munitions List and U.S. Munitions Import List), or transferred without any required license.

- Put in place a gate in your Returns and Repairs department, to make sure that all returns of defense articles to the U.S. are properly authorized (exemption claimed) and returned pursuant to license or exemption. Also make sure the department recognizes if the item has ended up in the hands of an unlicensed end user.

- 8) Create a technology control plan to cover controlled technology, and be sure to include IT, human resources, and procurement/purchasing (for offshore procurement) departments in your plan. Put in place measures to identify, correctly label, and protect controlled technology. Create Standard Operating Procedures (SOPs) to do so with the assistance of IT, HR, and procurement departments.

- 9) Create a license management system, including the export process and filing of Automated Export Records, to ensure compliance with all licenses, license exceptions (EAR), or license exemptions (ITAR).

- 10) Be sure to screen all customers against the restricted party lists, both at the initial customer input stage and prior to shipment, record, and preserve screens.

- 11) Train personnel for red flags of prohibited end use and diversion and create a process for resolution of red-flag screening.

- 12) Create a problem management to deal with issues as they arise, as well as government inquiries and visits.

- 13) Put all of the aforementioned procedures into a compliance manual and SOPs.

- 14) Train and test all personnel, or at least most personnel, on the compliance manual and SOPs on a regular basis.

- 15) Audit regularly, alternating responsible internal auditors (if you have them) with experienced outside auditors. Follow up on audit results. File voluntary disclosures where warranted.

Sidebar 1 | Export compliance attorney Kay Georgi shares 15 tips for ITAR export compliance.

proper authorizations. "We may never know the true extent of data loss in the U.S. involving controlled data and technology."

#### **Avoiding mistakes**

Companies and individuals can avoid the attention of export compliance enforcement officials by avoiding some common mistakes. Many of the large prime contractors have strong compliance programs in place, yet individuals at those companies still slip up when it comes to the ITAR. (For steps to setting up a compliance program see Sidebar 1.)

"Typical mistakes these individuals make include not paying enough attention to export compliance, as they are so busy with running the business they don't devote the time necessary to analyze the export control issues associated with a particular transaction," Georgi says. Another is that when an issue arises, they fail to consult legal counsel in-house or outside for assistance. "This is particularly an issue with respect to government inquiries, but it is also true in the case of 'Oops, I think we may have made a mistake." A third error is when they assume "they know the export compliance rules and [proceed] without appropriate guidance. If the experts need to check and double-check their advice, the employee who has sat in on an hour of training should not be making the decisions. They need to troubleshoot and take it to the responsible company (empowered) official or legal department."

Smaller companies and ones new to the defense market are also prone to easily avoidable ITAR compliance slip-ups. Georgi lists 10 of them:

- 1) Not realizing their work is subject to ITAR or EAR controls in the first place;

- 2) Not realizing that even if they do not export, they have to register as manufacturers if they manufacture defense articles in the U.S.:

- Not knowing which of their projects are ITAR, either because they don't ask the right questions or they don't have the size or knowledge to obtain the necessary information from their (usually much larger) customers with ITAR projects;

- Not realizing that even if they don't export end product outside the U.S., they can be exporting ITAR-controlled technical data when they procure build-to-spec or build-to-print parts from foreign suppliers or even U.S. suppliers with foreign suppliers;

- Not realizing that even if they don't export end product outside the U.S., they can be exporting ITAR-controlled technical data when they employ foreign nationals on their ITAR projects;

- Not devoting enough or the right resources to ITAR and EAR compliance;

- Too much reliance on a single export compliance official or a fraction of an employee (too-many-hats issue) and not enough training to that person;

- Not providing all the information needed for a complete and accurate license application;

- Not following all the provisos/conditions and the regulations in general in exporting pursuant to a license; and

- 10) Not handling export compliance issues properly, causing them to become larger export compliance issues. **MES**

#### Mil Tech Trends

RAD-HARD ELECTRONICS FOR MIL SPACE SYSTEMS

#### **Military** satellite payload performance demands drive rad-hard **electronics**

By John McHale, Editorial Director

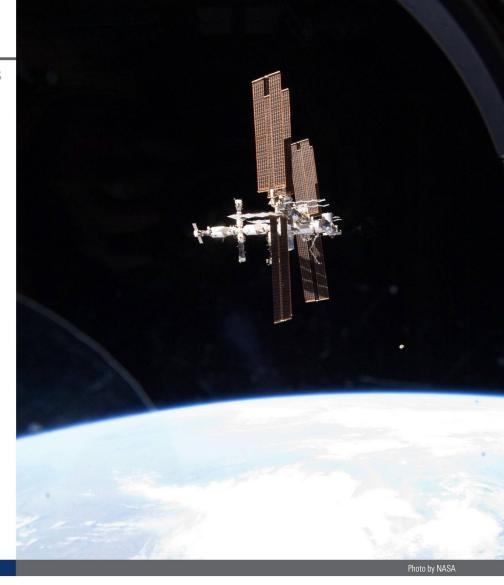

Increased ISR and communications bandwidth demands for military satellites are forcing rad-hard electronics designers to pack more and more performance into smaller form factors. Meanwhile, uncertainty reigns in terms of funding for space-based programs out of the DoD and NASA.

Battlefield success or success in any endeavor for that matter often is dependent on who has the best intelligence. Even as the U.S. military starts scaling back troop deployments in the Middle East, they will continue to increase their Intelligence, Surveillance, and Reconnaissance (ISR) operations to stay one step ahead of enemies and even allies.

Powerful ISR payloads enabled by the supercomputing performance of modern processors and computers are being developed and deployed in manned and unmanned ground, sea, air, and especially space platforms. All of these platforms have requirements demanding more and more performance with less power in ever-shrinking footprints, but the environmental challenges of space add difficulty as each component must be sufficiently radiation hardened, or rad hard, to survive for decades.

"Military space customers are facing pressures similar to commercial customers when it comes to performance require-

ments," says Ken O'Neill, Director of Space Marketing at Microsemi SOC Products Group in San Jose, CA. "Systems need ICs to have higher functionality and higher performance without consuming excessive power. They essentially want to have more functionality in less space.

There is demand for more processing, more bandwidth, and more memory for increased on-orbit storage, says Chuck Tabbert, Vice President of Sales and Marketing at Ultra Communications in Vista, CA. The increased performance requirements will be realized by making use of advanced FPGAs and multicore processors. There also seems to be a strong road map for increasing processing bandwidth by moving more toward fiber-optic technology, Tabbert says. "We are getting requests from customers for 40 Gb box-to-box connectivity over fiber because you can't move that kind of bandwidth over copper." Tabbert's company designs fiber-optic rad-hard transceivers and just patented a rad-hard 40 Gb transceiver.

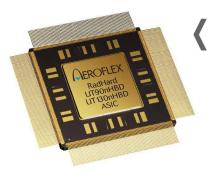

"The advanced technologies are driving our creativity when it comes to managing all the heat and power they generate as we jam more and more performance into 5- and 10-pound bags," says Tony Jordan, Director of Standard Products at Aeroflex Colorado Springs in Colorado Springs, CO. "Satellite weight has always been [an] issue. Every pound is tens of thousands of dollars of boost launch cost."

"Payload performance demands drive most of the technological change in satellites today," says Peter Milliken, Director of Semi-Custom Products at Aeroflex Colorado Springs. Applications such as signals intelligence and visual imaging are where the technology is going, he adds.

"There is increased pressure on all programs to deliver to the field new technology and on time. However, the debt problem worldwide is restricting satellite growth," Jordan says. "If not for the debt, the bandwidth demand would

be insatiable. Governments and satellite designers want to bring more capability to bear for satellite payloads, transponders, radios, and add features with the capability for remote sensing to have constant 'eyes in the sky.' While I cannot comment on classified programs, they continue to drive technology and are probably under less funding pressure, as they are not as visible as unclassified programs," he adds.

A great example of a Department of Defense (DoD) satellite using existing and new technologies together is the Lockheed Martin Advanced EHF satellite. which "uses eight RAD750s (Figure 1) for the payload with two RAD6000s used on the bus," says Vic Scuderi, Manager of Satellite Electronics for BAE Systems in Manassas, VA. It is a more conservative satellite design that takes a stable bus architecture and marries it with a newer generation payload. The RAD6000 adds stability at the bus level, while the RAD750 provides the necessary processing horsepower for the demanding payload requirements.

There are military space programs (tactical programs, short response time programs) needing parts that combine reprogrammability and high functionality with sufficient radiation tolerance for the mission (usually short duration and Low Earth Orbit), O'Neill continues. "Shorter missions have lesser radiation requirements. Our RTAX-DSP parts are seeing adoption in systems [that] need the additional signal processing horsepower afforded by built-in radiation tolerant multiply-accumulate blocks. The blocks provide higher density, giving users built-in DSP capability in the FPGA to perform signal-processing functions such as Fast Fourier Transforms (FFTs) more efficiently."

There also seems to be a big thrust toward affordability, to scale back some of the requirements to be more cost efficient without compromising reliability, Tabbert says. There might be times where integrators will take a little risk to lower costs, he adds.

#### Reliability still important

While many terrestrial programs leverage commercial technology right off the shelf, designers of space systems

Figure 1 | RAD750 single board computers from BAE Systems come in 3U and 6U form factors.

do not often have that luxury. Unlike in a ground vehicle or aircraft, electronic components that are used for satellite control must work for 15 years without failing - as satellites can't go back "to port" for maintenance. Suppliers must

be able to demonstrate to government customers that they have the legacy and stability in producing rad-hard electronics, as they will need to support programs that last for decades.

#### **High reliability IO boards** designed to work for you.

Through our work with aerospace quality assurance experts, we have developed proven strategies and a rigorous design and build process. If you need boards to perform in harsh

#### Try our free loaner boards.

If their high resolution, high reliability, high speed, low drift, low noise, and optional conduction cooling doesn't impress you, send it back at no charge. Our boards support most form factors.

environments where failure is not an option, contact our engineers who will work with you to select or customize analog, digital, or other boards for you.

#### Get our free software drivers.

We offer free drivers for Windows, Linux, and LabVIEW. Visit our website to check availability of other drivers.

Contact our engineers.

1-800-653-9970 quotes@generalstandards.com

#### **General Standards Corporation**

www.generalstandards.com/hirel

#### **BAE Systems to develop** Freescale QorlQ technology for space

Engineers at BAE Systems in Manassas, VA, have licensed processing technology from Freescale for use in radiation-hardened computers for space.

"We've licensed IP from Freescale" -Power Architecture, the QorlQ platform System-on-Chip (SoC) - as a follow-on to the RAD750, says David Rea, Product Manager at BAE Systems. "The QorlQ platform is compatible from a software perspective with the RAD6000 and RAD750. We will build the QorlQ platform processors at the 45 nanometer level."

According to a BAE Systems release, the Freescale technology will increase onboard satellite processing by as much as 10 times the current rate, enabling new payload and bus applications that were unthinkable in years past. The QorlQ platform includes features such as CoreNet and OCeaN fabrics, memory elements, memory controller, and high-speed interfaces.

"Power management is important for us, and we will take advantage of the inherent power savings of the QorlQ platform and add even more power management features," Rea continues. "Hardening the device typically is a two-year process. We started the process in the middle of last year and expect to have a qualified product by the middle of 2014. The power tweaks will be added at the circuit level as BAE Systems hardens the Freescale IP for highradiation environments. We harden the device using Rad-Hard by Design techniques. We have 150 nanometers in our fab in Manassas, VA, and relationships with IBM foundries at 90 and 45 nanometers," Rea says. "The IBM foundries are located in Burlington, VT and East Fishkill, NY."

Sidebar 1 | BAE takes QorlQ into space.

Figure 2 | The UT90nHBD ASIC from Aeroflex Colorado Springs is payload centric with strong radiation immunity.

"High performance components are meeting the payload needs but do not need to be as durable as satellite Command Data and Handling (CD&H) electronics, which keep the satellite on orbit," Milliken says. "CD&H devices require more radiation immunity than typically comes in an ASIC technology such as our UT90nHBD, which is payload centric (Figure 2). We also continue to still sell 5-volt technology that is used in legacy platforms of our aerospace and defense customers."

BAE Systems products typically work without ground prevention for as long as 15 years because they are designed to be rad hard from the ground up, Scuderi says. "Integrators that decide to go with commercial products and upscreen them to be rad hard are taking a risk when it comes to reliability. While the importance of flight heritage cannot be overemphasized, higher-performance payload applications demand higher processing and throughput. Our government customers are mindful of the need to mature this technology for space. Our processor technology road map has been funded to develop newer technologies with smaller and smaller feature sizes that translate directly to lower power and higher MIPS [Millions of Instructions Per Second]. Our newest 45 nanometer technology is a good example of this trend." For more on BAE Systems' rad-hard components, see Sidebar 1.

"Our hybrid DC/DC converter and filter customers are increasingly requiring a more complete capability in the components they procure," says Matthew Twitchell, Product Manager - Interpoint Space at Crane Aerospace & Electronics in Everett, WA. "The military space and commercial space markets have shifted from a narrow list of radiation requirements to requiring guarantees in several areas relating to radiation or a summation of effects. Some of these areas include analysis and measured test results for lower dose rates, which are more representative of the space environment - single event upsets, proton fluence, and some higher total radiation doses. These requirements drive the design methods and technologies used in creating the latest products as well as the need to conduct further testing and analysis for existing offerings."

"The design trend overall is moving toward higher levels of integration, including the use of radiation-guaranteed ICs and inherently rad-hard device technologies, such as SiC, SOI [Silicon on Insulator], and GaN," says Jay Kuehny, Principal Engineer, Crane Aerospace & Electronics. "While higher levels of integration serve lower cost and higher densities, great care must be taken to ensure robustness to single event effects. This often includes long design and qualification cycles and can result in high levels of redundancy, ultimately driving a more costly solution. To support the growing trend of longer-life spacecraft, these ICs must also be available to support program durations measured in decades rather than years. With the military and space markets extending program life expectations and the desire for proven technology, we have noted a slower rate of adoption for newer designs."

Crane's latest Interpoint converter product is the MFP Series point-of-load converter, Twitchell says. This device is guaranteed to 100 krad total radiation dose, Enhanced Low Dosed Radiation Susceptibility (ELDRS) level of 30 krad, to an LET of 85MeV-cm<sup>2</sup>/mg for single event effects and is Space Qualified to Class K per MIL-PRF-38534 on a Defense

Logistics Agency's (DLA's) Standard Microcircuit Drawing (SMD) number.

#### Other rad-hard offerings

VPT engineers have added a 15 A pointof-load DC-DC converter to their family of power conversion products for space applications. The SVGA0515 Series is a non-isolated, regulated buck converter, which steps down the voltage at the point of use in a distributed power system. It is qualified to MIL-PRF-38534 Class H and Class K by the Defense Logistics Agency and is targeted for power systems used on GEO, MEO, LEO, and deep-space applications.

The latest rad-hard FPGA offering from Xilinx is the Virtex-5QV FPGA, built on the second-generation ASMBLTM column-based architecture of the Virtex-5 FPGA family. It has protection from Single Event Upsets (SEUs), Single Event Transients (SETs), Single Event Latchup (SEL), and high Total Ionizing Dose (TID) – 1Mrad (Si). The device has 131,072 logic cells, is an integrated highspeed SERDES solution for space, and has 18 channels of >3 GHz multi-gigabit serial transceivers enabling high bandwidth for chip-to-chip, board-to-board, and box-to-box communications. For more rad-hard suppliers, see Sidebar 2.

#### Funding for space

Despite the increasing demands for performance on the payloads, funding for space programs from the DoD and other government agencies remains uncertain or flat at best for the next few years.

"What we're observing in the U.S. DoD market is a lot of uncertainty about when funding for procurement will be released, which makes it harder to forecast business," O'Neill says. "The uncertainty also causes hesitation on the contractor's part when releasing purchase orders. However, design activity seems to be relatively unaffected and remains constant with substantial activity going on in various programs."

"DoD funding trends have generally slowed many existing space programs [that] were previously very active in the procurement phase," Twitchell says. "This has translated into some shifting in the timing but has not yet materialized into cancelations. Recent DoD funding shifts have influenced the market by slowing the expected growth rates with our traditional customers. While the medium- to short-term growth rates seem to have flattened, it is expected that the commercial market and new partners in the space arena will begin to increase demand for space-qualified components. While this trend or shift to the commercial approach looks promising, the requirements for testing, analysis, and guarantees for product performance continue to increase. These [three] factors in combination look to provide us a very interesting next few years in the space market."

"DoD budgets are not yet beginning to slow on programs, because procurement for programs to be released in 2012, 2013 has been completed already," says Minal Sawant, Segment Marketing Manager at Microsemi. "The effects of budget cuts will be seen in 2014 and beyond, since programs are being put on hold."

"Budget cuts have impacted DoD and NASA missions, but we are fortunate that our business model includes a strong mix of commercial satellite opportunities as well," Twitchell says. "The commercial market has been holding steady across the international scene, and we have benefitted from this stability. Secondary payloads for DoD applications will also pave the way for government and commercial satellite ventures that are able to bring newer technologies into space." MES

#### Rad-hard company listings

Aeroflex Colorado Springs www.aeroflex.com/radhard

Aitech

www.rugged.com

Aldec

www.aldec.com

Atmel

www.atmel.com

**BAE Systems**

www.baesystems.com

C-MAC MicroTechnology

www.cmacapi.com

Corwil Technology Corp.

www.corwil.com

Crane Aerospace & Electronics

www.interpoint.com

**Curtiss-Wright Controls Defense Solutions**

www.cwcdefense.com

Harris

www.harris.com

Honeywell Microelectronics

www.honeywellmicroelectronics.com

Integra Technologies

www.integra-tech.com

International Rectifier

www.irf.com

Intersil Corp.

www.intersil.com

Jaz Semiconductor

www.jazzsemi.com

Linear Technology Corp.

www.linear.com

**Maxwell Technologies**

www.maxwell.com

Microelectronics Research Development Corp.

www.micro-rdc.com

Micropac Industries

www.micropac.com

www.microsemi.com

**Modular Devices** www.mdipower.com

MS Kennedy

www.mskennedy.com

**Novocell Semiconductor** www.novocellsemi.com

Peregrine Semiconductor Corp.

www.psemi.com

Ridgetop Group www.ridgetopgroup.com

Robust Chip, Inc.

www.robustchip.com

**Rochester Electronics**

www.rocelec.com

Semicoa

www.semicoa.com

Silicon Space Technology

www.siliconspacetech.com

www.silvaco.com/government/index.html

**STMicroelectronics**

www.st.com

Synopsys

www.synopsys.com

Synova

www.synova.com

Teledyne Microelectronic Technologies

www.teledynemicro.com

Texas Instruments

www.ti.com/home\_p\_hirel

**TRAD**

www.trad.fr

**Triad Semiconductor**

www.triadsemi.com

Ultra Communications www.ultracomm-inc.com

**VPT**

www.vpt-inc.com

Xilinx

www.xilinx.com

Sidebar 2 | Many companies are supplying rad-hard space electronics.

#### Mil Tech Trends

RAD-HARD ELECTRONICS FOR MIL SPACE SYSTEMS

#### Rad-hard SRAM FPGAs enable vast improvements in space exploration

By John D. Corbett and Gary M. Swift

As purpose-built Radiation Hard (RH) ASICs fall farther and farther behind in device technology and with their associated development costs and risks spiraling out of control, SRAM-based FPGAs present an ever-more attractive alternative for space applications and systems, also beating out traditional microprocessors and microcontrollers, DSPs, or One-Time Programmable (OTP) FPGAs.

Space environments have high levels of ionizing radiation that create complex design challenges for military systems engineers. Thus, electronic systems used in space must have circuitry that is highly reliable and able to endure extreme amounts of radiation. In space, it isn't a matter of if electronics will encounter radiation but how much, how often, and how will the device deal with each exposure to radiation. A single charged particle in space can knock thousands of electrons loose, causing electronic noise and signal spikes that can, if unchecked, cause systems to malfunction.

While design and system-level mitigation can ensure the proper operation of military spacecraft and instruments, high reliability and high availability are much easier to achieve with Radiation Hard (RH) components. High reliability is especially critical in systems such as the

processing circuitry that runs command and control - the telecommunications system in charge of telemetry to and from ground control where a failure can jeopardize the entire mission. Increasingly, government and private agencies deploying spacecraft are turning to SRAM-based FPGAs to perform these vital processing tasks because their capabilities have dramatically outpaced the traditional custom ASIC or One-Time Programmable (OTP) FPGA approaches.

Rad-hard SRAM-based FPGAs are giving space system designers a compelling set of performance, feature, and flexibility advantages for their new projects. The all-programmable nature of SRAM-based FPGAs enables the capabilities of a system to be improved and expanded even after launch when physical access is no longer possible. The hardware-programmable nature of

FPGAs makes them even more flexible than stand-alone processors such as microprocessors, DSPs, and microcontrollers that are only software programmable. What's more, the largest FPGAs can provide the function of multiple processors and other devices, all on a single chip.

Currently two types of FPGAs are used in space applications: anti-fuse-based one-time programmable FPGAs and SRAM-based reprogrammable FPGAs. Each type of device has its advantages and disadvantages. The anti-fuse-based devices have fewer programmable elements and thus fewer elements that can be upset by radiation. In addition, spacegrade anti-fuse devices make extensive use of redundant circuitry. Their relative simplicity and familiarity provide reassurance to space system designers and project managers.

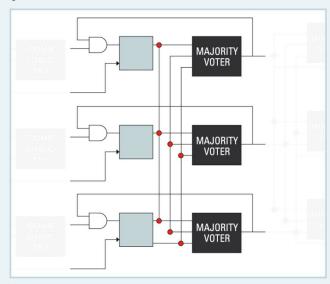

However, like RH ASICs, anti-fuse devices are not available in smaller process geometries such as 90 nm or 65 nm and thus have much lower capacity and performance than SRAM-based devices. SRAM-based devices enjoy a multiple-generation advantage in process geometry, thus offering greater capacity and performance, while consuming less power per gate. SRAM-based devices require configuration each time they are powered-on, and radiation-tolerant, SRAM-based devices may require more extensive error mitigation in the design implementation, such as adding Triple Modular Redundancy (TMR) or error correcting codes.

On the flip side, upset mitigation can be applied selectively where most needed in a reconfigurable FPGA (versus a nonreconfigurable OTP FPGA approach), thus making better use of resources. While configuration at startup adds complexity to the system, it also adds flexibility; last-minute requirement changes and bug fixes can be accommodated even when shortcomings are not apparent until after launch. The Virtex-5QV FPGA reduces the complexity of error mitigation in SRAM-based FPGAs by replacing the traditional 6-transistor configuration memory cell with a rad-hard-bydesign, 12-transistor cell that is about 1,000x harder to upset than commercial SRAM cells. Thus, SRAM-based FPGAs are useful in myriad space applications (See Sidebar 1 and also Figure 1).

#### FPGAs conquer another frontier

It's difficult to overstate the value an FPGA can offer in a space-bound system application. Once deployed, there is little or no ability to make hands-on hardware changes, so the programmability of an SRAM-based FPGA is a huge benefit. To be sure, microprocessors and microcontrollers can also be reprogrammed. But FPGAs excel in data-flow applications where functions such as packet inspection or signalprocessing algorithms implemented in hardware logic offer far more processing throughput than traditional microprocessors. And the FPGA hardware can be easily reconfigured to support new algorithms.

To deploy FPGAs in space applications, however, designers have to understand the environment and learn how to mitigate issues that affect reliability.

Figure 1 | FPGAs have proven useful in many space applications.

#### Upset hardening in hardware

SRAM-based FPGAs are now offered as fully radiation-hard components. That reduces or eliminates the need to use TMR in space designs and thus frees up space on the FPGA for design teams to integrate more functions with lower payload weight, power consumption, and system cost while improving functionality and sophistication of their systems.

To create these radiation-hard SRAMbased FPGA devices, a variety of techniques is used to implement the underlying FPGA memory and circuit elements in the device. Hardening the 35 million configuration cells and the 81,920 user flip-flops was accomplished with a self-redundant storage circuit that has double the typical number of transistors. The result is that susceptibility to SEU in space radiation environments was improved by 1,000x validating the circuit choice and the optimization of its layout, which involved fabricating many variants and subjecting them to in-beam irradiation tests.

In addition, all the clock, data, and asynchronous inputs to the flip-flops are protected with programmable filters to suppress single-event transients. Internal control circuitry was upset hardened to reduce troublesome SEFIs by 100x to practically zero where "practically zero" is defined as an expected rate of less often than once every 10,000 years.

Consequentially, design teams can now use SRAM-based FPGAs that are fully characterized for space radiation effects in heavy ion and proton environments and will withstand a TID of 1,000 krad(Si), guaranteed based on Test Method 1019 as defined in MIL-STD-833. That's more than triple the TID rating of radiation-tolerant OTP or typical SRAM-based FPGAs.

Sidebar 1 | To be useful in space applications, FPGAs must be radiation hardened.

A number of radiation-induced effects have been identified as a problem area for space-based designs:

- Single Event Upsets (SEUs)

- Single Event Transients (SETs)

- Single Event Functional Interrupts (SEFIs)

- Single Event Latchups (SELs)

- > Total Ionizing Dose (TID)

Of the radiation effects listed here, the latter two are particularly troublesome because they are destructive; consequently, space engineers require components with proven SEL immunity and large TID margins (2x or 3x) to cover extreme space weather they might encounter. The other three single-event effects might cause temporary

#### **FPGA Acceleration**